یک وضعیت رقابتی[ ۱] ( به انگلیسی: Race Condition ) یا Race Hazard یک نقص در سیستم الکترونیکی یا رایانه ای است که به موجب آن نتیجهٔ خروجی And یا Or به طور غیرمنتظره ای به زمانبندی و ترتیب رویدادهای دیگر بستگی دارد. این اصطلاح در اصل به حالتی گفته می شود که دو سیگنال با هم رقابت می کنند تا هر یک زودتر به خروجی تأثیر بگذارند.

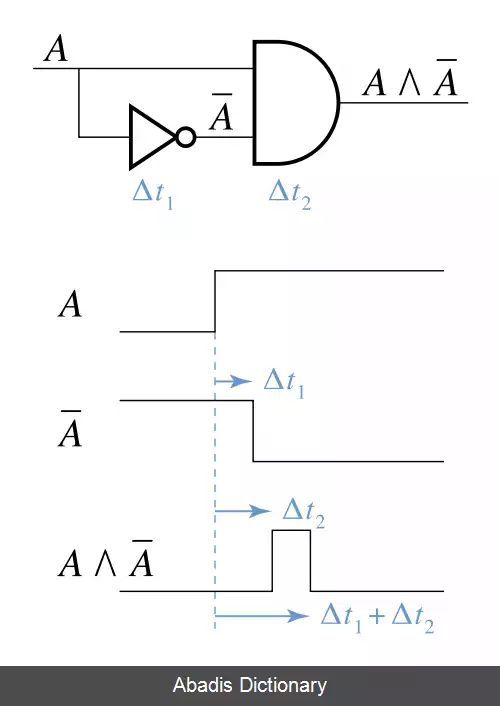

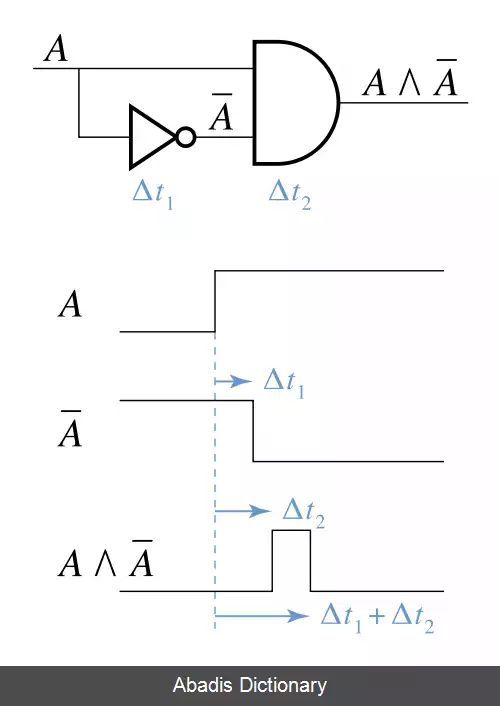

به عنوان مثال، یک دروازه And با دو ورودی که در یک ورودی با سیگنال A و در ورودی دیگر با سیگنال Á تغذیه می شود. در این تئوری خروجی هیچ وقت نباید یک شود. هر چند که، اگر تغییر در مقدار A از مقدار انتشار به ورودی دوم بیشتر طول بکشد، هنگامی که مقدار A از صفر به یک تغییر پیدا کند، در یک زمان کوتاه، هر دو ورودی در حالت یک قرار می گیرد و همچنین خروجی دروازه نیز مقدار یک می شود.

وضعیت رقابتی در نرم افزار هنگامی ناشی می شود که پردازش های مختلفی به یک وضع مشترک بستگی داشته باشد. به عنوان مثال بگذارید دو رشته T۱ و T۲ را فرض کنیم. هر کدام مقدار سراسری i را می خواهند یک واحد اضافه کنند. به طور ایده آل، مجموعه دستورهای زیر باید انجام شود:

• integer i=۰ ( حافظه )

• T۱ مقدار i را از حافظه خوانده و به Register۱ انتقال می دهد.

• T۱ مقدار i را که در Register۱ است، یک واحد اضافه می کند. Register1=۱

• T۱ مقدار Register۱ را در حافظه ذخیره می کند. i=۱

• T۲ مقدار i را از حافظه خوانده و به Register۲ انتقال می دهد.

• T۲ مقدار i را که در Register۲ است، یک واحد اضافه می کند. Register2=۲

• T۲ مقدار Register۲ را در حافظه ذخیره می کند. i=۲

• i=۲

در حالت بالا همان طور که انتظار می رفت مقدار i مساوی ۲ است، با این که، اگر دو رشته به طور هم زمان و بدون قفل کردن داده و همگام سازی اجرا شوند، خروجی دستور باید اشتباه شود که مجموعه دستورهای دیگر زیر این سناریو را نشان می دهد:

• integer i=۰ ( حافظه )

• T۱ مقدار i را از حافظه خوانده و به Register۱ انتقال می دهد.

• T۲ مقدار i را از حافظه خوانده و به Register۲ انتقال می دهد.

• T۱ مقدار i را که در Register۱ است، یک واحد اضافه می کند. Register1=۱

• T۲ مقدار i را که در Register۲ است، یک واحد اضافه می کند. Register2=۱

• T۱ مقدار Register۱ را در حافظه ذخیره می کند. i=۱

• T۲ مقدار Register۲ را در حافظه ذخیره می کند. i=۱

• i=۱

این نوشته برگرفته از سایت ویکی پدیا می باشد، اگر نادرست یا توهین آمیز است، لطفا گزارش دهید: گزارش تخلفبه عنوان مثال، یک دروازه And با دو ورودی که در یک ورودی با سیگنال A و در ورودی دیگر با سیگنال Á تغذیه می شود. در این تئوری خروجی هیچ وقت نباید یک شود. هر چند که، اگر تغییر در مقدار A از مقدار انتشار به ورودی دوم بیشتر طول بکشد، هنگامی که مقدار A از صفر به یک تغییر پیدا کند، در یک زمان کوتاه، هر دو ورودی در حالت یک قرار می گیرد و همچنین خروجی دروازه نیز مقدار یک می شود.

وضعیت رقابتی در نرم افزار هنگامی ناشی می شود که پردازش های مختلفی به یک وضع مشترک بستگی داشته باشد. به عنوان مثال بگذارید دو رشته T۱ و T۲ را فرض کنیم. هر کدام مقدار سراسری i را می خواهند یک واحد اضافه کنند. به طور ایده آل، مجموعه دستورهای زیر باید انجام شود:

• integer i=۰ ( حافظه )

• T۱ مقدار i را از حافظه خوانده و به Register۱ انتقال می دهد.

• T۱ مقدار i را که در Register۱ است، یک واحد اضافه می کند. Register1=۱

• T۱ مقدار Register۱ را در حافظه ذخیره می کند. i=۱

• T۲ مقدار i را از حافظه خوانده و به Register۲ انتقال می دهد.

• T۲ مقدار i را که در Register۲ است، یک واحد اضافه می کند. Register2=۲

• T۲ مقدار Register۲ را در حافظه ذخیره می کند. i=۲

• i=۲

در حالت بالا همان طور که انتظار می رفت مقدار i مساوی ۲ است، با این که، اگر دو رشته به طور هم زمان و بدون قفل کردن داده و همگام سازی اجرا شوند، خروجی دستور باید اشتباه شود که مجموعه دستورهای دیگر زیر این سناریو را نشان می دهد:

• integer i=۰ ( حافظه )

• T۱ مقدار i را از حافظه خوانده و به Register۱ انتقال می دهد.

• T۲ مقدار i را از حافظه خوانده و به Register۲ انتقال می دهد.

• T۱ مقدار i را که در Register۱ است، یک واحد اضافه می کند. Register1=۱

• T۲ مقدار i را که در Register۲ است، یک واحد اضافه می کند. Register2=۱

• T۱ مقدار Register۱ را در حافظه ذخیره می کند. i=۱

• T۲ مقدار Register۲ را در حافظه ذخیره می کند. i=۱

• i=۱

wiki: وضعیت رقابتی