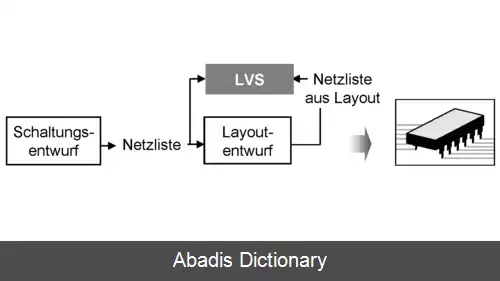

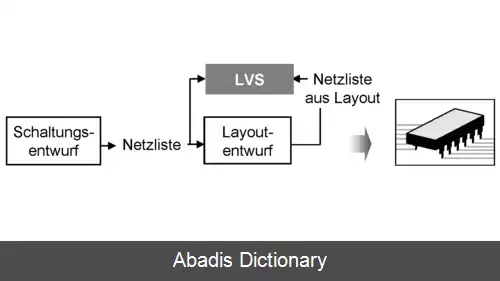

جانمایی درمقابل طرح واره ( LVS ) طبقه ای از نرم افزار تأیید خودکارسازی طراحی الکترونیکی ( EDA ) است که تعیین می کند آیا یک جانمایی مدار مجتمع خاص به طرح واره یا نمودار مدار اصلی طرح مطابقت دارد یا خیر.

یک بررسی قانون طراحی ( DRC ) موفق این اطمینان را می دهد که جانمایی با قوانین طراحی شده/مورد نیاز برای تولید بدون نقص تطابق داشته باشد. اگرچه تضمین نخواهد کرد که واقعاً مدار مورد نظر شما برای تولید را ارائه دهد. این جایی است که یک بررسی LVS مورد استفاده قرار می گیرد.

نرم افزار بررسی LVS اشکال کشیده شده جانمایی را شناسایی می کند که اجزاء الکتریکی مدار را به خوبی ارتباط بین آنها نشان می دهد. سپس نرم افزار آنها را با طرح کلی یا نمودار مدار مقایسه می نماید.

بررسی LVS شامل سه مرحله زیر می باشد:

• استخراج: این برنامه نرم افزاری یک فایل پایگاه داده شامل تمام لایه های کشیده شده می گیرد تا مدار را ضمن جانمایی نمایش دهد. سپس پایگاه داده را از طریق تعداد زیادی از عملیات منطقی اجرا می کند تا اجزاء نیم رسانای نشان داده شده در ترسیم توسط لایه های ساختمان را مشخص کند؛ و سپس لایه های فلزی کشیده شده مختلف را می آزماید و نحوه اتصال هر یک از این اجزاء با دیگران را می یابد.

• کاهش: در طی کاهش نرم افزار در صورت امکان اجزاء استخراج شده را در مجموعه های سری و موازی ترکیب کرده و یک نمایش فهرست شبکه ای از پایگاه داده جانمایی را نشان می دهد.

• مقایسه: فهرست شبکه ای جانمایی استخراج شده سپس با فهرست شبکه ای گرفته شده از طرح کلی مدار مقایسه می شود. اگر دو فهرست شبکه ای تطابق داشته باشند، سپس مدار در بررسی LVS قبول می گردد که در این صورت بی نقص از لحاظ LVS خوانده می شود.

در اکثر موارد در اولین باری که مهندس جانمایی نیاز به آزمودن گزارش های نرم افزار لوس دارد جانمایی در لوس قبول نمی شود و تغییراتی در جانمایی ایجاد می کند. نمونه خطاهای مواجه شده طی لوس عبارتند از:

• اتصال های کوتاه: دو یا چند سیم که نباید به یکدیگر متصل باشند با یکدیگر اتصال دارند و باید جدا شوند.

• اتصال های باز: دو یا چند سیم که باید به یکدیگر متصل باشند آویزان رها شده یا تنها در قسمتی با یکدیگر اتصال دارند و باید به درستی متصل شوند تا این مشکل برطرف شود.

• اجزاء نامتناسب: اجزاء از یک نوع اشتباه استفاده شده اند. ( به عنوان مثال یک قطعه MOS با ولتاژ آستانه پایین به جای یک قطعه MOS با ولتاژ آستانه استاندارد )

• اجزاء فراموش شده: یک جزء مورد انتظار خارج از جانمایی رها شده.

• خطاهای در ویژگی: یک جزء در اندازه اشتباه در مقایسه با طرح کلی است.

این نوشته برگرفته از سایت ویکی پدیا می باشد، اگر نادرست یا توهین آمیز است، لطفا گزارش دهید: گزارش تخلفیک بررسی قانون طراحی ( DRC ) موفق این اطمینان را می دهد که جانمایی با قوانین طراحی شده/مورد نیاز برای تولید بدون نقص تطابق داشته باشد. اگرچه تضمین نخواهد کرد که واقعاً مدار مورد نظر شما برای تولید را ارائه دهد. این جایی است که یک بررسی LVS مورد استفاده قرار می گیرد.

نرم افزار بررسی LVS اشکال کشیده شده جانمایی را شناسایی می کند که اجزاء الکتریکی مدار را به خوبی ارتباط بین آنها نشان می دهد. سپس نرم افزار آنها را با طرح کلی یا نمودار مدار مقایسه می نماید.

بررسی LVS شامل سه مرحله زیر می باشد:

• استخراج: این برنامه نرم افزاری یک فایل پایگاه داده شامل تمام لایه های کشیده شده می گیرد تا مدار را ضمن جانمایی نمایش دهد. سپس پایگاه داده را از طریق تعداد زیادی از عملیات منطقی اجرا می کند تا اجزاء نیم رسانای نشان داده شده در ترسیم توسط لایه های ساختمان را مشخص کند؛ و سپس لایه های فلزی کشیده شده مختلف را می آزماید و نحوه اتصال هر یک از این اجزاء با دیگران را می یابد.

• کاهش: در طی کاهش نرم افزار در صورت امکان اجزاء استخراج شده را در مجموعه های سری و موازی ترکیب کرده و یک نمایش فهرست شبکه ای از پایگاه داده جانمایی را نشان می دهد.

• مقایسه: فهرست شبکه ای جانمایی استخراج شده سپس با فهرست شبکه ای گرفته شده از طرح کلی مدار مقایسه می شود. اگر دو فهرست شبکه ای تطابق داشته باشند، سپس مدار در بررسی LVS قبول می گردد که در این صورت بی نقص از لحاظ LVS خوانده می شود.

در اکثر موارد در اولین باری که مهندس جانمایی نیاز به آزمودن گزارش های نرم افزار لوس دارد جانمایی در لوس قبول نمی شود و تغییراتی در جانمایی ایجاد می کند. نمونه خطاهای مواجه شده طی لوس عبارتند از:

• اتصال های کوتاه: دو یا چند سیم که نباید به یکدیگر متصل باشند با یکدیگر اتصال دارند و باید جدا شوند.

• اتصال های باز: دو یا چند سیم که باید به یکدیگر متصل باشند آویزان رها شده یا تنها در قسمتی با یکدیگر اتصال دارند و باید به درستی متصل شوند تا این مشکل برطرف شود.

• اجزاء نامتناسب: اجزاء از یک نوع اشتباه استفاده شده اند. ( به عنوان مثال یک قطعه MOS با ولتاژ آستانه پایین به جای یک قطعه MOS با ولتاژ آستانه استاندارد )

• اجزاء فراموش شده: یک جزء مورد انتظار خارج از جانمایی رها شده.

• خطاهای در ویژگی: یک جزء در اندازه اشتباه در مقایسه با طرح کلی است.

wiki: جانمایی درمقابل طرح واره