مدار آسنکرون. یک مدار آسنکرون یا خود زمان یک مدار منطقی دیجیتال ترتیبی است که به وسیلهٔ یک مدار کلاک یا کلاک مرجع کنترل نمی شود و به جای آن از سیگنال هایی استفاده می کند که بیان کننده اتمام دستورالعمل ها و عملیات هاست که به وسیلهٔ پروتکل های انتقال ساده داده مشخص می شوند. این نوع مدار در تضاد با مدارهای سنکرون است که درآن ها تغییر در مقادیر سیگنال در مدار به وسیلهٔ پالس های تکرار شونده که سیگنال کلاک نامیده می شوند، انجام می شود. امروزه بیش تر تجهیزات دیجیتالی از مدارهای سنکرون استفاده می کنند اگر چه مدارهای آسنکرون پتانسیل سریع تر بودن را دارند و ممکن است دارای مزایای مصرف انرژی کم تر، تداخل الکترومغناطیسی کم تر و ماژولار بهتر در سیستم های بزرگ باشند. مدارهای آسنکرون یک حوزهٔ فعال تحقیق در طراحی مدارهای منطقی هستند.

مدارهای منطقی می توانند به دو دستهٔ مدارهای منطقی ترکیبی ( در آن ها سیگنال خروجی فقط به سیگنال ورودی فعلی وابسته است ) ومنطق ترتیبی ( در آن ها خروجی هم به ورودی فعلی و هم به ورودی پیشین وابسته است ) تقسیم می شوند.

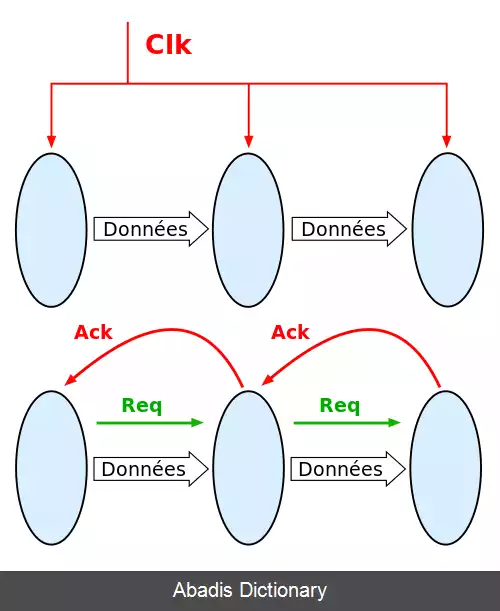

در مدارهای منطقی سنکرون یک اسیلاتور الکترونیکی یک سری تکرارشونده از پالس های هم اندازه را تولید می کنند که سیگنال کلاک نامیده می شود. سیگنال کلاک یاد شده به تمام المان های حافظه موجود در مدار که فلیپ - فلاپ نامیده می شود اعمال می شود. خروجی فلیپ - فلاپ ها فقط زمانی تغییر می کند که لبهٔ پالس کلاک ایجاد شود؛ بنابراین تغییرات در سیگنال های منطقی مدار همگی به صورت همزمان و در فاصلهٔ منظم همگام با کلاک انجام می شود. خروجی تمام اجزای مدار حالت مدار نامیده می شود.

حالت یک مدار سنکرون فقط با پالس کلاک تغییر می کند. تغییر در سیگنال نیز به مقدار مشخصی از زمان برای انتشار از طریق گیت های منطق ترکیبی مدار دارد که تأخیر انتشار نامیده می شود. دوره تناوب سیگنال کلاک به اندازهٔ کافی طول می کشد بنابراین خروجی تمام گیت های منطقی زمان کافی برای پایدار شدن مقادیرشان پیش از پالس کلاک بعدی را دارند. تا زمانی که این شرایط برآورده شود، مدارهای سنکرون به صورت پایدار عمل می کنند بنابراین طراحی این مدارها ساده است.

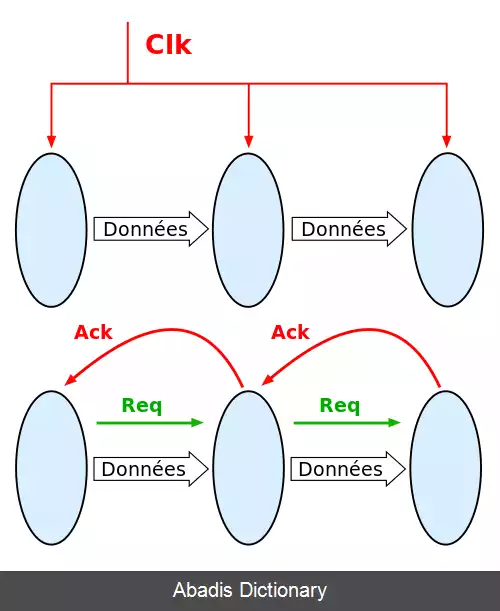

هرچند یک نقص مدارهای سنکرون این است که آهسته هستند. حداکثر سرعت کلاک ممکن به وسیلهٔ سیر منطقی با طولانی ترین تأخیر انتشار تعیین می شود که مسیر بحرانی نامیده می شود؛ بنابراین مسیرهای منطقی که سریعاً عملیات خود را به پایان می رسانند اغلب بیکار هستند. مشکل دیگر این است که سیگنال کلاکی که به طور گسترده توزیع شده است توان زیادی مصرف می کند و این عمل پیوسته انجام می شود خواه مدار ورودی بگیرد یا نگیرد. در مدارهای آسنکرون سیگنال کلاک وجود ندارد و حالت مدار به محض تغییر ورودی تغییر می کند. از آن جا که مدارهای آسنکرون برای پردازش ورودی مجبور به انتظار برای یک پالس کلاک نیستند، می توانند از مدارهای سنکرون سریع تر باشند و سرعت آن ها از نظر تئوری فقط با تأخیر انتشار گیت های منطقی محدود می شود. با این حال طراحی مدارهای آسنکرون مشکل تر است و این مسئله ای است که در مدارهای سنکرون وجود ندارد. این موضوع به این دلیل است که حالت حاصل از یک مدار آسنکرون می تواند حساس به زمان رسیدن نسبی ورودی ها در گیت ها باشد. اگر انتقال دو ورودی در یک زمان تقریباً یکسان باشد، مدار ممکن است به حالت اشتباه وابسته به اختلاف ناشی از تأخیر انتشار گیت ها برود که به آن وضعیت رقابت می گویند. این وضعیت در مدارهای سنکرون بسیار کم تر است چرا که وضعیت رقابت فقط هنگامی می تواند رخ دهد که ورودی ها از خارج سیستم سنکرون باشند که ورودی های آسنکرون نامیده می شوند. اگر چه بعضی از سیستم های دیجیتال به صورت تماماً آسنکرون ساخته شده اند، امروزه مدارهای آسنکرون معمولاً در بخش های بحرانی مدارهای سنکرون استفاده می شوند و سرعت آن ها در مقیاس بالاتری است همچون مدارهای پردازش سیگنال.

این نوشته برگرفته از سایت ویکی پدیا می باشد، اگر نادرست یا توهین آمیز است، لطفا گزارش دهید: گزارش تخلفمدارهای منطقی می توانند به دو دستهٔ مدارهای منطقی ترکیبی ( در آن ها سیگنال خروجی فقط به سیگنال ورودی فعلی وابسته است ) ومنطق ترتیبی ( در آن ها خروجی هم به ورودی فعلی و هم به ورودی پیشین وابسته است ) تقسیم می شوند.

در مدارهای منطقی سنکرون یک اسیلاتور الکترونیکی یک سری تکرارشونده از پالس های هم اندازه را تولید می کنند که سیگنال کلاک نامیده می شود. سیگنال کلاک یاد شده به تمام المان های حافظه موجود در مدار که فلیپ - فلاپ نامیده می شود اعمال می شود. خروجی فلیپ - فلاپ ها فقط زمانی تغییر می کند که لبهٔ پالس کلاک ایجاد شود؛ بنابراین تغییرات در سیگنال های منطقی مدار همگی به صورت همزمان و در فاصلهٔ منظم همگام با کلاک انجام می شود. خروجی تمام اجزای مدار حالت مدار نامیده می شود.

حالت یک مدار سنکرون فقط با پالس کلاک تغییر می کند. تغییر در سیگنال نیز به مقدار مشخصی از زمان برای انتشار از طریق گیت های منطق ترکیبی مدار دارد که تأخیر انتشار نامیده می شود. دوره تناوب سیگنال کلاک به اندازهٔ کافی طول می کشد بنابراین خروجی تمام گیت های منطقی زمان کافی برای پایدار شدن مقادیرشان پیش از پالس کلاک بعدی را دارند. تا زمانی که این شرایط برآورده شود، مدارهای سنکرون به صورت پایدار عمل می کنند بنابراین طراحی این مدارها ساده است.

هرچند یک نقص مدارهای سنکرون این است که آهسته هستند. حداکثر سرعت کلاک ممکن به وسیلهٔ سیر منطقی با طولانی ترین تأخیر انتشار تعیین می شود که مسیر بحرانی نامیده می شود؛ بنابراین مسیرهای منطقی که سریعاً عملیات خود را به پایان می رسانند اغلب بیکار هستند. مشکل دیگر این است که سیگنال کلاکی که به طور گسترده توزیع شده است توان زیادی مصرف می کند و این عمل پیوسته انجام می شود خواه مدار ورودی بگیرد یا نگیرد. در مدارهای آسنکرون سیگنال کلاک وجود ندارد و حالت مدار به محض تغییر ورودی تغییر می کند. از آن جا که مدارهای آسنکرون برای پردازش ورودی مجبور به انتظار برای یک پالس کلاک نیستند، می توانند از مدارهای سنکرون سریع تر باشند و سرعت آن ها از نظر تئوری فقط با تأخیر انتشار گیت های منطقی محدود می شود. با این حال طراحی مدارهای آسنکرون مشکل تر است و این مسئله ای است که در مدارهای سنکرون وجود ندارد. این موضوع به این دلیل است که حالت حاصل از یک مدار آسنکرون می تواند حساس به زمان رسیدن نسبی ورودی ها در گیت ها باشد. اگر انتقال دو ورودی در یک زمان تقریباً یکسان باشد، مدار ممکن است به حالت اشتباه وابسته به اختلاف ناشی از تأخیر انتشار گیت ها برود که به آن وضعیت رقابت می گویند. این وضعیت در مدارهای سنکرون بسیار کم تر است چرا که وضعیت رقابت فقط هنگامی می تواند رخ دهد که ورودی ها از خارج سیستم سنکرون باشند که ورودی های آسنکرون نامیده می شوند. اگر چه بعضی از سیستم های دیجیتال به صورت تماماً آسنکرون ساخته شده اند، امروزه مدارهای آسنکرون معمولاً در بخش های بحرانی مدارهای سنکرون استفاده می شوند و سرعت آن ها در مقیاس بالاتری است همچون مدارهای پردازش سیگنال.

wiki: مدار آسنکرون