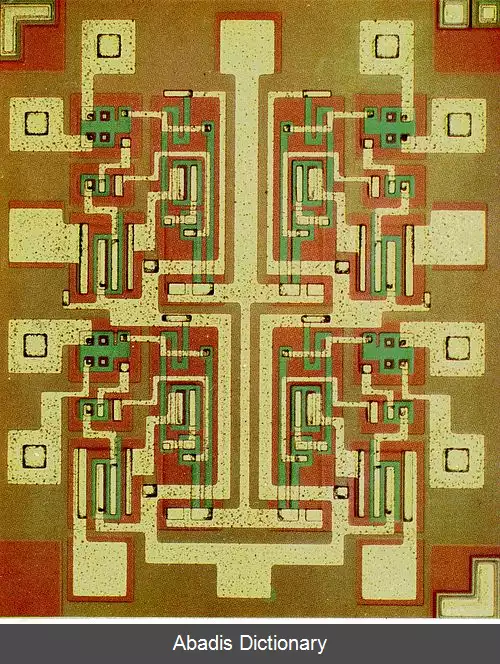

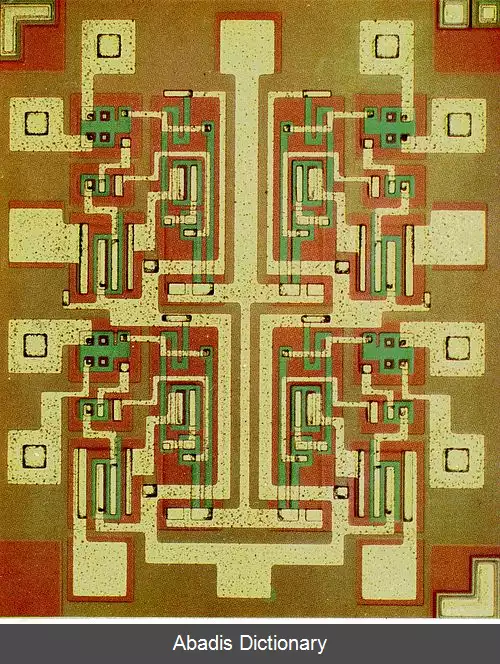

در ساخت نیم رسانا، فرایند ۲ نانومتری شکنج دای ماسفت بعدی پس از گره فرایند ۳ نانومتر است. از سال ۲۰۲۰، تی اس ام سی و اینتل هر دو محصولات ۲ نانومتری را در نقشه راه خود قرار داده اند که اولین تولید آن برای سال ۲۰۲۳ یا اخیراً برنامه ریزی شده است. از می ۲۰۲۲، تی اس ام سی قصد دارد تولید ۲ نانومتری را در پایان سال ۲۰۲۴ و تولید انبوه را در سال ۲۰۲۵ آغاز کند؛[ ۱] [ ۲] اینتل تولید را در سال ۲۰۲۴، [ ۳] و سازنده تراشه کره جنوبی سامسونگ در سال ۲۰۲۵ را پیش بینی می کند.

در اواخر سال ۲۰۱۸، رئیس تی اس ام سی، مارک لیو پیش بینی کرد که مقیاس بندی تراشه تا ۳ نانومتر و گره های ۲ نانومتر ادامه یابد؛[ ۴] با این حال، از سال ۲۰۱۹، سایر متخصصان نیم رسانا در مورد اینکه آیا گره های بیش از ۳ نانومتر می توانند موفقیت آمیز باشند، بلاتکلیف بودند. [ ۵]

تی اس ام سی در سال ۲۰۱۹ تحقیق در مورد ۲ نانومتر را آغاز کرد. [ ۶] تی اس ام سی انتظار دارد هنگام جابجایی از ۳ نانومتر به ۲ نانومتر، انواع ترانزیستورهای فین فت به جی ای ای فت انتقال یابد. [ ۷] در مه سال ۲۰۲۱ آی بی ام اعلام کرد که به فناوری ساخت ۲ نانومتری دست یافته است. [ ۸]

این نوشته برگرفته از سایت ویکی پدیا می باشد، اگر نادرست یا توهین آمیز است، لطفا گزارش دهید: گزارش تخلفدر اواخر سال ۲۰۱۸، رئیس تی اس ام سی، مارک لیو پیش بینی کرد که مقیاس بندی تراشه تا ۳ نانومتر و گره های ۲ نانومتر ادامه یابد؛[ ۴] با این حال، از سال ۲۰۱۹، سایر متخصصان نیم رسانا در مورد اینکه آیا گره های بیش از ۳ نانومتر می توانند موفقیت آمیز باشند، بلاتکلیف بودند. [ ۵]

تی اس ام سی در سال ۲۰۱۹ تحقیق در مورد ۲ نانومتر را آغاز کرد. [ ۶] تی اس ام سی انتظار دارد هنگام جابجایی از ۳ نانومتر به ۲ نانومتر، انواع ترانزیستورهای فین فت به جی ای ای فت انتقال یابد. [ ۷] در مه سال ۲۰۲۱ آی بی ام اعلام کرد که به فناوری ساخت ۲ نانومتری دست یافته است. [ ۸]

wiki: فرایند ۲ نانومتر