عایق بندی تاشه کم عمق ( STI ) ( به انگلیسی: Shallow trench isolation ) ، که به عنوان تکنیک عایق بندی جعبه ای نیز شناخته می شود، یک ویژگی مدار مجتمع است که از نشت جریان الکتریکی بین اجزای ادوات نیم رسانای مجاور جلوگیری می کند. STI عموماً در گره های فناوری فرایند سیماس ۲۵۰ نانومتر و کوچکتر استفاده می شود. فناوری های قدیمی سیماس و فناوری های غیر ماس معمولاً از جداسازی بر اساس لوکوس استفاده می کنند. [ ۱]

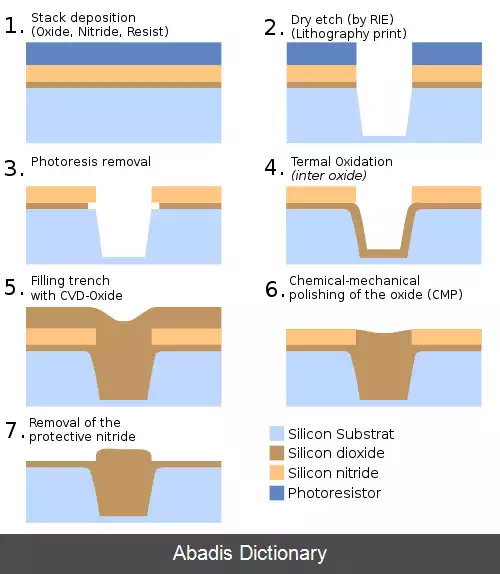

STI در مراحل اولیه ساخت ادوات نیم رسانا، قبل از شکل گیری ترانزیستورها ایجاد می شود. مراحل کلیدی فرایند STI شامل زدایش یک الگوی تاشه در سیلیکون، رسوب دهی یک یا چند ماده دی الکتریک ( مانند دی اکسید سیلیکون ) برای پُرکردن تاشه ها و حذف دی الکتریک اضافی با استفاده از تکنیکی مانند مسطح سازی شیمیایی - مکانیکی است .

برخی از فناوری های ساخت نیم رسانا نیز شامل عایق بندی تاشه عمیق هستند، این ویژگی اغلب در مدارهای مجتمع آنالوگ یافت می شود.

اثر لبه تاشه باعث ایجاد آنچه اخیراً «اثر کانال باریک وارون»[ ۲] یا «اثر عرض باریک وارون» نامیده می شود، شده است. [ ۳] اساساً، به دلیل افزایش میدان الکتریکی در لبه، ایجاد یک کانال رسانا ( توسط وارونگی ) در ولتاژ کمتر آسان تر است. ولتاژ آستانه برای عرض ترانزیستور باریک به طور مؤثر کاهش می یابد. [ ۴] [ ۵] نگرانی اصلی قطعات الکترونیکی جریان نشت زیرآستانه است که پس از کاهش ولتاژ آستانه به میزان قابل توجهی بزرگتر می شود.

• نِهِشت ( به انگلیسی: deposition ) پشته ( اکسید + نیترید محافظ )

• چاپ سخت نگاری

• زدایش خشک ( زدایش یون فعال )

• پُرکردن تاشه با اکسید

• مسطح سازی شیمیایی - مکانیکی اکسید

• حذف نیترید محافظی

• میزان سازی ارتفاع اکسید به Si

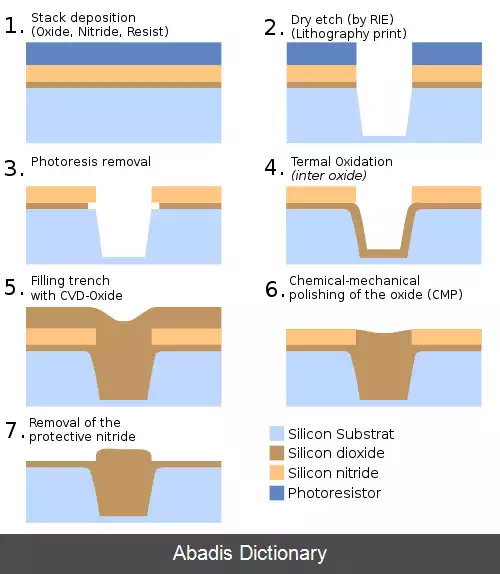

این نوشته برگرفته از سایت ویکی پدیا می باشد، اگر نادرست یا توهین آمیز است، لطفا گزارش دهید: گزارش تخلفSTI در مراحل اولیه ساخت ادوات نیم رسانا، قبل از شکل گیری ترانزیستورها ایجاد می شود. مراحل کلیدی فرایند STI شامل زدایش یک الگوی تاشه در سیلیکون، رسوب دهی یک یا چند ماده دی الکتریک ( مانند دی اکسید سیلیکون ) برای پُرکردن تاشه ها و حذف دی الکتریک اضافی با استفاده از تکنیکی مانند مسطح سازی شیمیایی - مکانیکی است .

برخی از فناوری های ساخت نیم رسانا نیز شامل عایق بندی تاشه عمیق هستند، این ویژگی اغلب در مدارهای مجتمع آنالوگ یافت می شود.

اثر لبه تاشه باعث ایجاد آنچه اخیراً «اثر کانال باریک وارون»[ ۲] یا «اثر عرض باریک وارون» نامیده می شود، شده است. [ ۳] اساساً، به دلیل افزایش میدان الکتریکی در لبه، ایجاد یک کانال رسانا ( توسط وارونگی ) در ولتاژ کمتر آسان تر است. ولتاژ آستانه برای عرض ترانزیستور باریک به طور مؤثر کاهش می یابد. [ ۴] [ ۵] نگرانی اصلی قطعات الکترونیکی جریان نشت زیرآستانه است که پس از کاهش ولتاژ آستانه به میزان قابل توجهی بزرگتر می شود.

• نِهِشت ( به انگلیسی: deposition ) پشته ( اکسید + نیترید محافظ )

• چاپ سخت نگاری

• زدایش خشک ( زدایش یون فعال )

• پُرکردن تاشه با اکسید

• مسطح سازی شیمیایی - مکانیکی اکسید

• حذف نیترید محافظی

• میزان سازی ارتفاع اکسید به Si

wiki: عایق بندی تاشه کم عمق