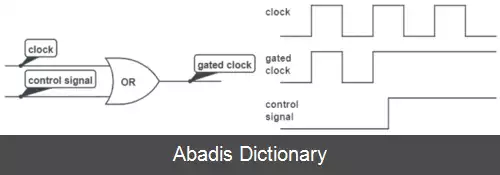

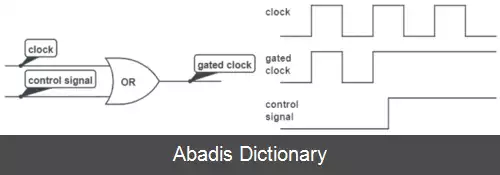

دروازه بندی ( قطع و وصل کردن متناوب ) ساعت یک تکنیک رایج است که در خیلی از مدارهای همگام برای کاهش هدر رفتن توان دینامیکی، با حذف کردن سیگنال ساعت زمانی که مدار در حال استفاده نیست یا سیگنال ساعت را نادیده می گیرد، استفاده می شود. دروازه بندی ( قطع و وصل کردن ) ساعت با هرس کردن درخت ساعت ، با افزودن منطق های بیشتر به مدار ساخته شده در مصرف انرژی صرفه جویی می کند. هرس ساعت بخش هایی از مدرا را غیر فعال میکند تا فلیپ فلاپ های موجود در آنها دیگر نیازی به تغییر حالت ندارند. تغییر دادن حالت ها انرژی استفاده می کند. زمانی که فلیپ فلاچ ها در حال تغییر نیستند، مصرف انرژی مقیاس بندی به صفر می رسد و فقط منجر به جریان های نشتی می شود. [ ۱]

اگرچه مدارهای ناهمگام طبق تعریفشان "ساعت" جهانی ندارند، اما اصطلاح دروازه بندی ساعت کامل را استفاده میکنند تا نشان دهند تکنیک های مختلف دروازه بندی و قطع و وصلی ساعت تنها تقریبی از رفتار وابسته به داده نشان داده شده توسط مدارهای ناهمگام هستند . زمانی که میزانه ای که در آن کسی ساعت یک مدار همگام را دروازه می کند به صفر نزدیک می شود، مصرف برق آن مدار به مدار ناهمگام نزدیک می شود: مدار انتقال منطق ها را تنها زمانی که به طور فعال در حال محاسبه است، تولید می کند. [ ۲]

یک راه حل جایگزین برای دروازه بندی ساعت استفاده از منطق فعال سازی ساعت ( CE ) در مسیر داده همگام سازی شده است که از مالتی پلکسر ورودی استفاده میکند، به طور مثال، برای فلیپ فلاپ نوع دی با استفاده از نماد گذاری زبان C/ Verilog به صورت Dff= CE? D: Q ؛ که در آن : Dff ورودی D از فلیپ فلاپ نوع D است و D مقیاس اطلاعات ورودی است ( بدون ورودی CE ) Q، نیز خروجی فلیپ فلاپ نوع D است. این نوع از دروازه بندی ساعت بدون شرایط مسابقه است و برای طراحی های FPGA و برای دروازه بندی ساعی مدار های کوچک ترجیح داده میشود. برای طراحی های FPGA فلیپ فلاچ های نوع D یک ورودی سیگنال CE اضافه دارد.

دروازه بندی ساعت با استفاده کردن حالت های متوصل به ثبات ها کار میکند و انها را برای دروازه بندی کردن ساعت استفاده میکند. یک طراحی باید از این شرایط فعال سازی برخوردار باشد تا تواند از دروازه بندی ساعت بهره مند شود. این فرایند دروازه بندی ساعت میزان زیادی از انرژی و سطح استفاده شده را کم میکند . زیرا تعداد زیادی از تسهیم کننده ها را حذف کرده و با منطق دروازه بندی ساعت جایگزین میکند . این منطق دروازه بندی ساعت عموما به صورت سلول های «دروازه ساعت یکپارچه» ( ICG ) است. هرچند منطق دروازه بندی ساعت درخت ساختار ساعت را تغییر میدهد از آنجایی که منطق دروازه بندی ساعت در درخت ساعت پیاده سازی میشود.

این نوشته برگرفته از سایت ویکی پدیا می باشد، اگر نادرست یا توهین آمیز است، لطفا گزارش دهید: گزارش تخلفاگرچه مدارهای ناهمگام طبق تعریفشان "ساعت" جهانی ندارند، اما اصطلاح دروازه بندی ساعت کامل را استفاده میکنند تا نشان دهند تکنیک های مختلف دروازه بندی و قطع و وصلی ساعت تنها تقریبی از رفتار وابسته به داده نشان داده شده توسط مدارهای ناهمگام هستند . زمانی که میزانه ای که در آن کسی ساعت یک مدار همگام را دروازه می کند به صفر نزدیک می شود، مصرف برق آن مدار به مدار ناهمگام نزدیک می شود: مدار انتقال منطق ها را تنها زمانی که به طور فعال در حال محاسبه است، تولید می کند. [ ۲]

یک راه حل جایگزین برای دروازه بندی ساعت استفاده از منطق فعال سازی ساعت ( CE ) در مسیر داده همگام سازی شده است که از مالتی پلکسر ورودی استفاده میکند، به طور مثال، برای فلیپ فلاپ نوع دی با استفاده از نماد گذاری زبان C/ Verilog به صورت Dff= CE? D: Q ؛ که در آن : Dff ورودی D از فلیپ فلاپ نوع D است و D مقیاس اطلاعات ورودی است ( بدون ورودی CE ) Q، نیز خروجی فلیپ فلاپ نوع D است. این نوع از دروازه بندی ساعت بدون شرایط مسابقه است و برای طراحی های FPGA و برای دروازه بندی ساعی مدار های کوچک ترجیح داده میشود. برای طراحی های FPGA فلیپ فلاچ های نوع D یک ورودی سیگنال CE اضافه دارد.

دروازه بندی ساعت با استفاده کردن حالت های متوصل به ثبات ها کار میکند و انها را برای دروازه بندی کردن ساعت استفاده میکند. یک طراحی باید از این شرایط فعال سازی برخوردار باشد تا تواند از دروازه بندی ساعت بهره مند شود. این فرایند دروازه بندی ساعت میزان زیادی از انرژی و سطح استفاده شده را کم میکند . زیرا تعداد زیادی از تسهیم کننده ها را حذف کرده و با منطق دروازه بندی ساعت جایگزین میکند . این منطق دروازه بندی ساعت عموما به صورت سلول های «دروازه ساعت یکپارچه» ( ICG ) است. هرچند منطق دروازه بندی ساعت درخت ساختار ساعت را تغییر میدهد از آنجایی که منطق دروازه بندی ساعت در درخت ساعت پیاده سازی میشود.

wiki: دروازه بندی ساعت