حافظه نهان CPU یا همان کش سی پی یو نوعی حافظهٔ سخت افزاری است که توسط واحد پردازنده مرکزی کامپیوتر برای کاهش هزینه ( زمان یا انرژی ) میانگین دسترسی به دادهٔ حافظه اصلی استفاده می شود. در واقع کش یک حافظه کوچک تر و سریع تر است که در نزدیکی یک هستهٔ پردازنده قرار گرفته است و کپی هایی از داده هایی از مکان های حافظه اصلی که مکرراً استفاده می شوند را ذخیره می کند. بیشتر CPUها دارای یک سلسله مراتب از چندین سطح حافظه نهان هستند ( L1، L2، گاهی L3 و بندرت L4 ) هستند و در سطح یک، حافظه های نهان مخصوص - دستورالعمل و مخصوص - داده به صورت مجزا قرار دارند.

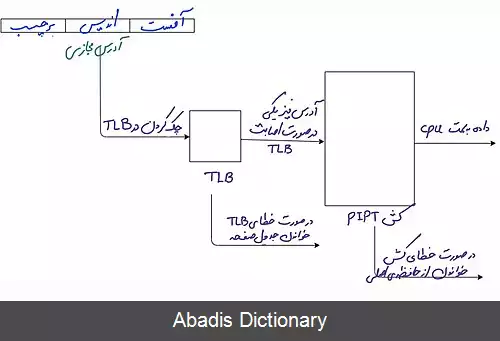

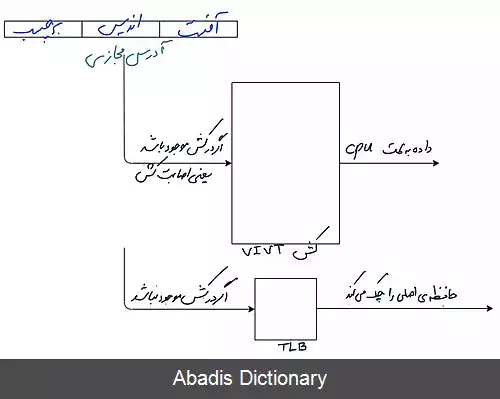

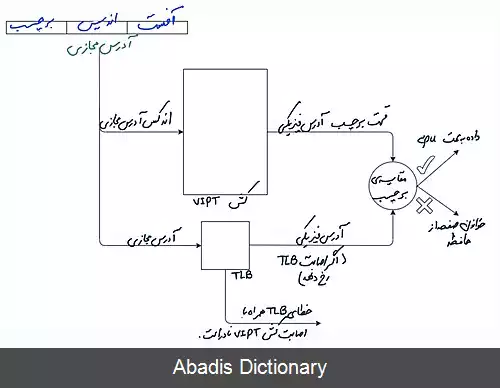

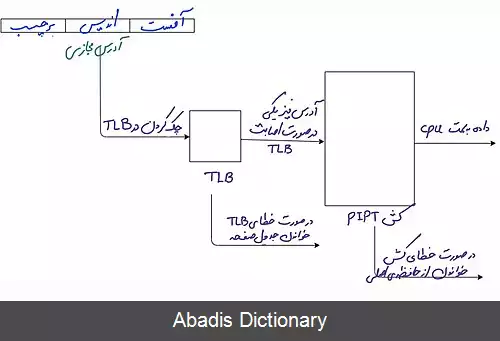

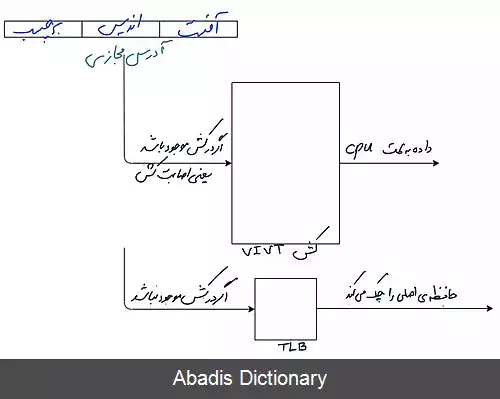

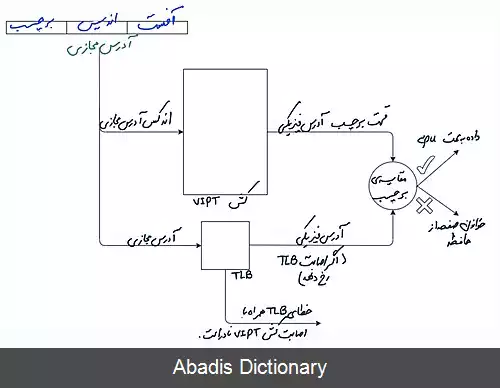

انواع دیگری از کش ها وجود دارند ( که جزو اندازهٔ کش مهمترین کش های ذکر شده در بالا محسوب نمی شوند ) ، همچون بافر مرجع ترجمه ( translation lookaside buffer ) که بخشی از واحد مدیریت حافظه است که در بسیاری از CPUها وجود دارد. به TLB گاهی کش ترجمهٔ آدرس نیز می گویند.

زمانی که پردازنده سعی می کند تا یک مکان در حافظه اصلی را بخواند یا در یک مکان از حافظه اصلی بنویسد، اول چک می کند که آیا دادهٔ مربوط به مکان مورد نظر در حال حاضر در کش وجود دارد یا خیر. اگر وجود داشت، پردازنده از روی کش می خواند یا در آن می نویسد و به سراغ حافظه اصلی که بسیار کندتر است نمی رود.

اکثر پردازنده های جدید رومیزی یا سرور، حداقل دارای ۳ کش مستقل هستند: یک کش دستورالعمل برای سرعت بخشیدن به واکشی دستورالعمل فایل یا برنامهٔ قابل اجرا، یک کش داده برای سرعت بخشیدن به واکشی و ذخیرهٔ داده، و یک بافر مرجع برای ترجمه ( translation lookaside buffer ) که برای سرعت بخشیدن به ترجمهٔ آدرس مجازی به فیزیکی، هم برای دستورالعمل های فایل یا برنامهٔ قابل اجرا و هم برای داده استفاده می شود. می توان فقط یک TLB برای دسترسی به دستورالعمل ها و داده فراهم کرد، یا اینکه دو TLB مجزا، یکی برای دستورالعمل ( ITLB ) و دیگری برای داده ( DTLB ) فراهم کرد. کش داده معمولاً به شکل سلسله مراتبی از سطوح بیشتر کش ( L1، L2، و … ) سازماندهی می شود. با این وجود، کش TLB جزئی از واحد مدیریت حافظه ( MMU ) است و مستقیماً به کش های پردازنده مربوط نمی شود.

تاریخچه اولیه فناوری کش تقریباً مصادف با ابداع و استفاده از حافظه مجازی است. به خاطر قیمت بالای نیمه رساناها در دهه ۱۹۶۰ کامپیوترها به سمت استفاده از حافظه مجازی سوق پیدا کردند. در روزهای اولیه سرعت دسترسی به حافظه تنها مقدار کمی با رجیستر فرق داشت ولی در دهه ۱۹۸۰ با ساخت پردازنده های پرسرعت شکاف سرعت بین پردازنده و حافظه بسیار بیشتر شد که این موضوع باعث پدید آمدن حافظه های میانی از جمله کش شد.

این نوشته برگرفته از سایت ویکی پدیا می باشد، اگر نادرست یا توهین آمیز است، لطفا گزارش دهید: گزارش تخلفانواع دیگری از کش ها وجود دارند ( که جزو اندازهٔ کش مهمترین کش های ذکر شده در بالا محسوب نمی شوند ) ، همچون بافر مرجع ترجمه ( translation lookaside buffer ) که بخشی از واحد مدیریت حافظه است که در بسیاری از CPUها وجود دارد. به TLB گاهی کش ترجمهٔ آدرس نیز می گویند.

زمانی که پردازنده سعی می کند تا یک مکان در حافظه اصلی را بخواند یا در یک مکان از حافظه اصلی بنویسد، اول چک می کند که آیا دادهٔ مربوط به مکان مورد نظر در حال حاضر در کش وجود دارد یا خیر. اگر وجود داشت، پردازنده از روی کش می خواند یا در آن می نویسد و به سراغ حافظه اصلی که بسیار کندتر است نمی رود.

اکثر پردازنده های جدید رومیزی یا سرور، حداقل دارای ۳ کش مستقل هستند: یک کش دستورالعمل برای سرعت بخشیدن به واکشی دستورالعمل فایل یا برنامهٔ قابل اجرا، یک کش داده برای سرعت بخشیدن به واکشی و ذخیرهٔ داده، و یک بافر مرجع برای ترجمه ( translation lookaside buffer ) که برای سرعت بخشیدن به ترجمهٔ آدرس مجازی به فیزیکی، هم برای دستورالعمل های فایل یا برنامهٔ قابل اجرا و هم برای داده استفاده می شود. می توان فقط یک TLB برای دسترسی به دستورالعمل ها و داده فراهم کرد، یا اینکه دو TLB مجزا، یکی برای دستورالعمل ( ITLB ) و دیگری برای داده ( DTLB ) فراهم کرد. کش داده معمولاً به شکل سلسله مراتبی از سطوح بیشتر کش ( L1، L2، و … ) سازماندهی می شود. با این وجود، کش TLB جزئی از واحد مدیریت حافظه ( MMU ) است و مستقیماً به کش های پردازنده مربوط نمی شود.

تاریخچه اولیه فناوری کش تقریباً مصادف با ابداع و استفاده از حافظه مجازی است. به خاطر قیمت بالای نیمه رساناها در دهه ۱۹۶۰ کامپیوترها به سمت استفاده از حافظه مجازی سوق پیدا کردند. در روزهای اولیه سرعت دسترسی به حافظه تنها مقدار کمی با رجیستر فرق داشت ولی در دهه ۱۹۸۰ با ساخت پردازنده های پرسرعت شکاف سرعت بین پردازنده و حافظه بسیار بیشتر شد که این موضوع باعث پدید آمدن حافظه های میانی از جمله کش شد.

wiki: حافظه نهان سی پی یو